# Geode™ CS4210 IEEE 1394 OHCl Controller

## **General Description**

The National Semiconductor<sup>®</sup> Geode<sup>™</sup> CS4210 is a PCI-based IEEE 1394 OHCI (Open Host Controller Interface) controller. The CS4210 provides an implementation of the IEEE 1394 Link Layer functionality according to the programming model defined by 1394 OHCI Specification Version 1.0. It supports high speed serial communication up to 400 Mbits per second.

The CS4210 is an implementation of the link layer protocol of the IEEE 1394 high speed serial bus, with additional features to support the transaction and bus management layers. The CS4210 also includes DMA engines for high speed performance data transfer and a host PCI bus interface. Perfect for use in PC, set-top box, thin client, and WebPAD™ system applications.

The CS4210 supports two types of data transfers: asynchronous and isochronous.

The CS4210 provides an external IEEE 1394 physical layer device interface. The CS4210's physical layer interface (PHY-Link) is compatible with the Geode™ CS4103 and other IEEE 1394 physical layer devices.

### **Features**

- Supports 100, 200, and 400 Mbit/sec data transfer rates

- Compliant with 1394 OHCI Specification Version 1.0

- Compatible interface with the Geode CS4103 IEEE

P1394a Physical Layer (PHY) device and other IEEE

1394-1995 version and P1394a Draft 2.0 Physical Layer devices

- Eight isochronous transmit contexts

- Eight isochronous receive contexts

- Capable of reading a 128-byte descriptor in one burst

- 128 byte, zero wait state bursting

- Dynamically re-prioritize services

- 2 KB of isochronous transmit FIFO

- 2 KB of asynchronous transmit FIFO

- 4 KB of receiver FIFO

- Per-packet FIFO thresholding

- Four concurrent posted writes

- Eight pending physical responses

- National specific configuration registers

- I<sup>2</sup>C interface support for an optional serial EEPROM

- Accepts and generates external 8 kHz reference clock

- 5V tolerant PCI rev 2.1 I/O interface

- 0.25µ CMOS

- 100-pin LQFP (Low-profile Quad Flat Pack) package

- NAND tree for test purposes

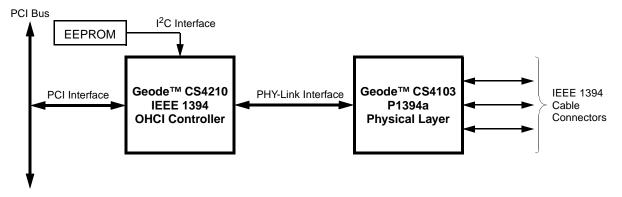

# System Block Diagram

National Semiconductor is a registered trademark of National Semiconductor Corporation.

Geode and WebPAD are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

# **Table of Contents**

| 1.0 | Arch | itectural Description6                                                                                       |

|-----|------|--------------------------------------------------------------------------------------------------------------|

|     | 1.1  | PCI INTERFACE MODULE                                                                                         |

|     | 1.2  | DMA ENGINE                                                                                                   |

|     |      | 1.2.1 Transfer Engine                                                                                        |

|     |      | 1.2.2 Host Memory Organization                                                                               |

|     |      | 1.2.3 ATDMA                                                                                                  |

|     |      | 1.2.4 ITDMA                                                                                                  |

|     |      | 1.2.5 RDMA                                                                                                   |

|     | 1.3  | TRANSMIT DRAIN                                                                                               |

|     | 1.4  | RECEIVE FILL                                                                                                 |

|     | 1.5  | LINK LAYER                                                                                                   |

|     | 1.6  | PHYSICAL LAYER INTERFACE                                                                                     |

|     | 1.7  | REGISTER SET                                                                                                 |

|     | 1.8  | RELATED DOCUMENTS                                                                                            |

|     | 1.0  | RELATED DOCOMENTS                                                                                            |

| 2.0 | Sign | al Definitions                                                                                               |

|     | 2.1  | PIN ASSIGNMENT                                                                                               |

|     | 2.2  | SIGNAL DESCRIPTIONS                                                                                          |

|     | 2.2  | 2.2.1 PCI Bus Interface Signals                                                                              |

|     |      | 2.2.2 PHY-Link Interface Signals                                                                             |

|     |      | 2.2.3 Miscellaneous Interface Signals                                                                        |

|     |      | 2.2.4 Power Supplies and Ground Connections                                                                  |

|     |      | 2.2.4 Tower oupplies and cround connections                                                                  |

| 3.0 | Oper | rational Description                                                                                         |

|     | 3.1  | OVERVIEW                                                                                                     |

|     |      | 3.1.1 Asynchronous Data Transfer Functions15                                                                 |

|     |      | 3.1.2 Isochronous Data Transfer Functions                                                                    |

|     |      | 3.1.3 Miscellaneous Functions                                                                                |

|     | 3.2  | SOFTWARE INTERFACE OVERVIEW16                                                                                |

|     |      | 3.2.1 Registers                                                                                              |

|     |      | 3.2.2 DMA Operation                                                                                          |

|     |      | 3.2.2.1 DMA Memory                                                                                           |

|     |      | 3.2.2.2 Physical Response DMA                                                                                |

|     |      | 3.2.3 Interrupts                                                                                             |

|     |      | 3.2.3.1 Asynchronous Transmit Interrupts                                                                     |

|     |      | 3.2.3.2 Asynchronous Receive Interrupts       16         3.2.3.3 Isoch Tx and Rx Context Interrupts       17 |

|     | 3.3  | COMMON DMA CONTROLLER FEATURES                                                                               |

|     | 0.0  | 3.3.1 Context Registers                                                                                      |

|     |      | 3.3.2 ContextControl.event                                                                                   |

|     |      | 3.3.2.1 ContextControl.run                                                                                   |

|     |      | 3.3.2.2 ContextControl.wake                                                                                  |

|     |      | 3.3.2.3 ContextControl.active                                                                                |

|     |      | 3.3.2.4 ContextControl.dead                                                                                  |

|     |      | 3.3.2.5 CommandPtr                                                                                           |

|     | 3.4  | LIST MANAGEMENT                                                                                              |

|     |      | 3.4.1 Context Initialization                                                                                 |

|     |      | 3.4.2 Appending to Running List                                                                              |

|     |      | 3.4.3 Stopping a Context                                                                                     |

|     |      | 3.4.4 Hardware Behavior                                                                                      |

|     |      |                                                                                                              |

#### Table of Contents (Continued) 3.5 3.5.1 3.5.2 3.5.3 3.5.4 3.5.5 3.6 3.6.1 3.6.2 3.6.3 3.6.4 3.6.5 Interrupt Considerations for Physical Requests .......27 3.6.6 3.7 3.7.1 3.7.2 3.7.2.2 3.7.2.3 3.7.3 3.7.4 3.7.5 3.7.6 3.7.7 3.8 3.8.1 3.8.2 3.8.3 3.9 3.9.1 4.0 4.1 4.2 4.3 4.4 OHCI CONFIGURATION REGISTERS ......48 4.4.1 4.4.2 4.4.3 4.4.4 4.4.5 4.4.6 Bus Identification Register ......61 4.4.7 4.4.8 4.4.9 4.4.10 PostedWriteAddress Register ......64 4.4.11 HCControl Register ......65 4.4.12

#### Table of Contents (Continued) 4.4.13 4.4.14 4.4.15 4.4.16 4.4.17 4.4.18 4.4.19 4.4.20 4.4.21 4.4.22 4.4.23 4.4.24 Asynchronous Request/Response Transmit ......80 4.4.25 4.4.26 4.4.26.1 4.4.26.2 Isoch Transmit Command Pointer......85 4.4.27 4.4.27.2 Isoch Receive Command Pointer Register.......88 4.4.27.3 Isoch Receive Context Match Register......88 4.5 4.5.1 4.5.2 nscEventSet/Clear ......93 4.5.3 nscMaskSet/Clear ......93 4.5.4 nscRAMBist ......94 4.5.5 4.5.6 nscTxThreshold ......94 4.5.7 4.5.8 nscPhysReadCount ......95 4.5.9 nscPhysWriteCount ......95 4.5.10 4.5.11 nscBusmgrID ......96 4.5.12 4.5.13 nscChanAvailHi ......96 nscChanAvailLo ......96 4.5.14

| Table of Contents (Continued) |                                 |                                                                                                                                                            |  |  |  |

|-------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5.0                           | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | trical Specifications. 97  NAND TREE TEST MODE .97  ABSOLUTE MAXIMUM RATINGS .98  OPERATING CONDITIONS .98  DC CHARACTERISTICS .99  AC SPECIFICATIONS .101 |  |  |  |

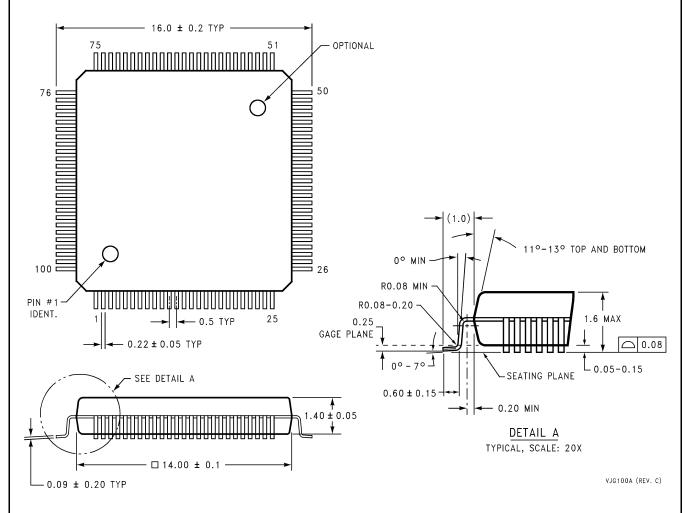

| 6.0                           |                                 | sical Dimensions 102                                                                                                                                       |  |  |  |

| 0.0                           | · iiy                           |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

|                               |                                 |                                                                                                                                                            |  |  |  |

# 1.0 Architectural Description

The CS4210 device implements an IEEE 1394 serial bus host controller as specified by the OHCI Specification Version 1.0. It is organized as a collection of reusable modules as illustrated in Figure 1-1.

The interface to the 1394 bus is organized into three clock domains: PCI, SCLK, and SCLK/2. The PCI clock domain can operate at up to 33 MHz. The PCI clock can also be stopped. The SCLK clock domain operates at 49.152 MHz. The SCLK/2 clock domain operates at 24.576 MHz.

### 1.1 PCI INTERFACE MODULE

The PCI interface module provides a full function bus mastering interface to the PCI bus.

### 1.2 DMA ENGINE

The DMA engine is decomposed into four functional modules:

- TE: Transfer Engine

- Provides generic data movement services to the rest of the DMA engine logic.

- ATDMA: Asynchronous Transmit DMA

- Controls the transmission of all asynchronous packets.

- ITDMA: Isochronous Transmit DMA

- Controls the transmission of all isochronous packets.

- · RDMA: Receive DMA

- Processes all received packets (asynchronous, isochronous and physical) and transmit status.

A single port SRAM is shared by the DMA logic for caching control information and descriptor blocks fetched from the host memory. This RAM is used for capturing entire descriptor blocks in a single PCI bus tenure.

Figure 1-1. Functional Block Diagram

# **Architectural Description (Continued)**

### 1.2.1 Transfer Engine

The transfer engine performs data movement between different sources/sinks:

- 1) Host memory (TxFIFOs/RxFIFO, Scratchpad SRAM)

- DMA modules (ATDMA, ITDMA, or RDMA)

All byte alignment and byte swapping tasks are also performed by the transfer engine.

### 1.2.2 Host Memory Organization

The 1394 OHCI specification allows for many different data FIFO implementations. This CS4210 implements two transmit FIFOs (asynchronous and isochronous) and a single receive FIFO. The transmit FIFOs share a single embedded dual-port SRAM (36x1024). The receive FIFO uses a single embedded dual-port SRAM (36x1024). A small transmit FIFO is also implemented using latches and some decoding logic.

All FIFOs may be tested using an embedded RAM BIST controller. See Section 4.5.4 "nscRAMBist" on page 94 for more details.

### 1.2.3 ATDMA

The ATDMA module controls the transmission of all asynchronous packets. This includes AT (Asynchronous Transmit) Request context packets, AT Response context packets and all physical DMA transmit request and response packets. The ATDMA module also controls retransmission of packets as required by the OHCI specification.

### 1.2.4 ITDMA

The ITDMA module controls the transmission of all isochronous packets. Annex E of the OHCI specification describes the operation of the ITDMA module. This annex was contributed by National Semiconductor.

### 1.2.5 RDMA

The RDMA module processes all received packets and transmit status. This includes packets destined for the AR (Asynchronous Receive) Request context, AR Response context, all IR (Isochronous Receive) contexts, the Self-ID buffer, and all physical DMA requests (including CSR accesses). It also examines the transmit status to manage the collection of currently active physical DMA requests.

### 1.3 TRANSMIT DRAIN

The transmit drain module accepts packets from the TxFIFOs (asynchronous and isochronous) and interfaces with the link layer module to transmit these packets. It also places transmit completion status in the TxFIFO.

### 1.4 RECEIVE FILL

The receive fill module accepts packets from the link layer and places them into the RxFIFO. It performs packet filtering and routing. It also determines which handshake, if any, to return for each received packet.

### 1.5 LINK LAYER

The link layer module implements a 1394 link layer function developed for this host controller application. It includes support for the CRC32 generation/checking, link state machine, transmit/receive data paths and the generation/reception of cycle start packets. This module includes support for features defined in the P1394a supplement.

### 1.6 PHYSICAL LAYER INTERFACE

The physical layer interface module implements the external interface to connect to the Geode CS4103 P1394a physical layer device. It includes support for features defined in revision 2.0 of the P1394a specification.

### 1.7 REGISTER SET

The register set module coordinates slave accesses to the host controller registers. It fields read/write requests from the PCI interface module. It can also read configuration data from a serial EEPROM device via an I<sup>2</sup>C interface.

### 1.8 RELATED DOCUMENTS

The following documents may be useful in understanding the terms and concepts used in this publication.

- 1394 Open Host Controller Interface Specification Release 1.0

- IEEE 1394-1995 High Performance Serial Bus, 1995

- ISO/IEC 13213:1994 Control and Status Register Architecture for Microcomputer Buses International Standards Organization, 1994

- IEEE P1394a Standard for a High Performance Serial bus (Supplement)

# 2.0 Signal Definitions

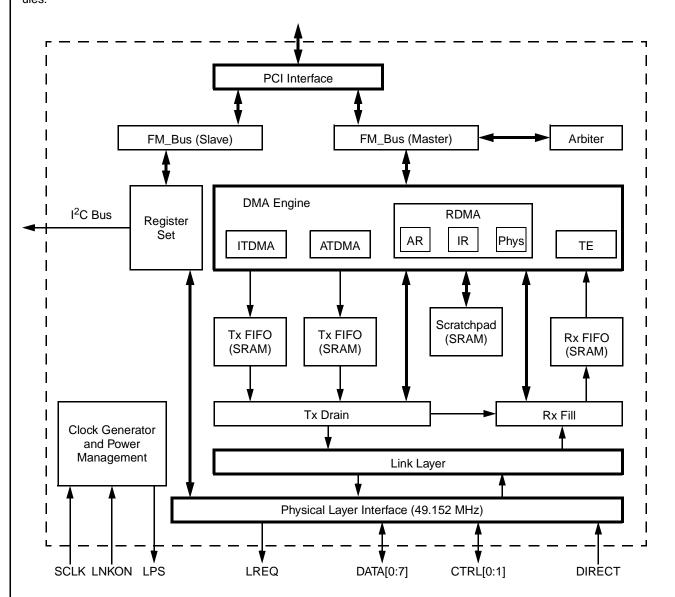

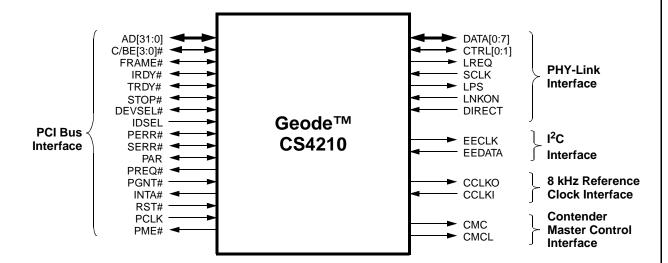

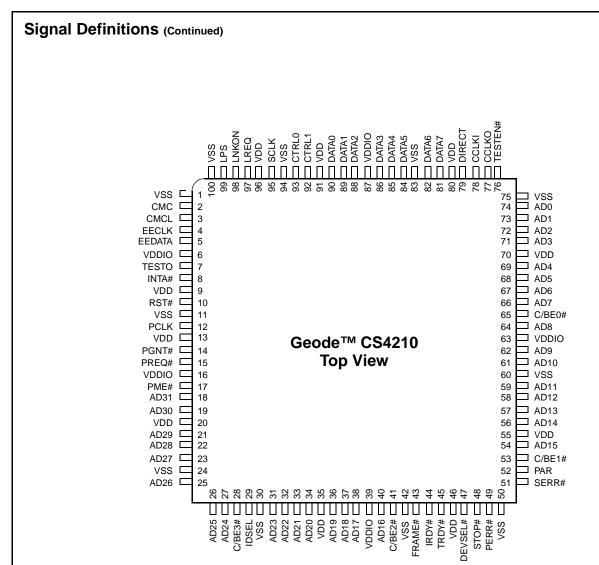

This section defines the signals and external interface of the CS4210. Figure 2-1 shows the pins organized by their functional groupings (internal test and electrical pins are not shown).

### 2.1 PIN ASSIGNMENT

The tables in this section use several common abbreviations. Table 2-1 lists the mnemonics and their meanings.

Figure 2-2 on page 9 shows the pin assignment for the CS4210 with Tables 2-2 and 2-3, on pages 10 and 11, listing the pin assignments sorted by pin number and alphabetically by signal name.

Section 2.2 "Signal Descriptions" starting on page 12 provides a description for each signal within its associated functional group.

Table 2-1. Pin Type Definitions

| Mnemonic | Definition             |

|----------|------------------------|

| I        | Input Pin              |

| I/O      | Bidirectional Pin      |

| 0        | Output                 |

| t/s      | TRI-STATE Signal       |

| VDD      | 2.5V Core Power Supply |

| VDDIO    | 3.3V I/O Power Supply  |

| VSS      | Ground Connection      |

Figure 2-1. Signal Groups

Figure 2-2. Pin Assignment Diagram Order Number: CS4210VJG

Table 2-2. Pin Assignment - Sorted by Pin Number

| No.         Signal         Type           1         VSS         GND           2         CMC         O           3         CMCL         O           4         EECLK         O           5         EEDATA         I           6         VDDIO         PWR           7         TESTO         O           8         INTA#         O           9         VDD         PWR           10         RST#         O           11         VSS         GND           12         PCLK         I           13         VDD         PWR           14         PGNT#         I           15         PREQ#         O           16         VDDIO         PWR           17         PME#         O           18         AD31         I/O           20         VDD         PWR           21         AD29         I/O           22         AD28         I/O           23         AD27         I/O           24         VSS         GND           25         AD26         I/O <t< th=""><th>Pin</th><th></th><th></th></t<> | Pin |        |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|

| 2       CMC       O         3       CMCL       O         4       EECLK       O         5       EEDATA       I         6       VDDIO       PWR         7       TESTO       O         8       INTA#       O         9       VDD       PWR         10       RST#       O         11       VSS       GND         12       PCLK       I         13       VDD       PWR         14       PGNT#       I         15       PREQ#       O         16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I                                                                                                                                    |     | Signal | Туре |

| 3         CMCL         O           4         EECLK         O           5         EEDATA         I           6         VDDIO         PWR           7         TESTO         O           8         INTA#         O           9         VDD         PWR           10         RST#         O           11         VSS         GND           12         PCLK         I           13         VDD         PWR           14         PGNT#         I           15         PREQ#         O           16         VDDIO         PWR           17         PME#         O           18         AD31         I/O           19         AD30         I/O           20         VDD         PWR           21         AD29         I/O           22         AD28         I/O           23         AD27         I/O           24         VSS         GND           25         AD26         I/O           26         AD25         I/O           27         AD24         I/O                                             | 1   | VSS    | GND  |

| 4       EECLK       O         5       EEDATA       I         6       VDDIO       PWR         7       TESTO       O         8       INTA#       O         9       VDD       PWR         10       RST#       O         11       VSS       GND         12       PCLK       I         13       VDD       PWR         14       PGNT#       I         15       PREQ#       O         16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND                                                                                                                              | 2   | CMC    | 0    |

| 5         EEDATA         I           6         VDDIO         PWR           7         TESTO         O           8         INTA#         O           9         VDD         PWR           10         RST#         O           11         VSS         GND           12         PCLK         I           13         VDD         PWR           14         PGNT#         I           15         PREQ#         O           16         VDDIO         PWR           17         PME#         O           18         AD31         I/O           19         AD30         I/O           20         VDD         PWR           21         AD29         I/O           22         AD28         I/O           23         AD27         I/O           24         VSS         GND           25         AD26         I/O           26         AD25         I/O           27         AD24         I/O           28         C/BE3#         I/O           29         IDSEL         I                                       | 3   | CMCL   | 0    |

| 6         VDDIO         PWR           7         TESTO         O           8         INTA#         O           9         VDD         PWR           10         RST#         O           11         VSS         GND           12         PCLK         I           13         VDD         PWR           14         PGNT#         I           15         PREQ#         O           16         VDDIO         PWR           17         PME#         O           18         AD31         I/O           19         AD30         I/O           20         VDD         PWR           21         AD29         I/O           22         AD28         I/O           23         AD27         I/O           24         VSS         GND           25         AD26         I/O           26         AD25         I/O           27         AD24         I/O           28         C/BE3#         I/O           29         IDSEL         I           30         VSS         GND                                       | 4   | EECLK  | 0    |

| 7         TESTO         O           8         INTA#         O           9         VDD         PWR           10         RST#         O           11         VSS         GND           12         PCLK         I           13         VDD         PWR           14         PGNT#         I           15         PREQ#         O           16         VDDIO         PWR           17         PME#         O           18         AD31         I/O           20         VDD         PWR           21         AD29         I/O           22         AD28         I/O           23         AD27         I/O           24         VSS         GND           25         AD26         I/O           26         AD25         I/O           27         AD24         I/O           28         C/BE3#         I/O           29         IDSEL         I           30         VSS         GND           31         AD23         I/O           32         AD22         I/O                                       | 5   | EEDATA | I    |

| 8       INTA#       O         9       VDD       PWR         10       RST#       O         11       VSS       GND         12       PCLK       I         13       VDD       PWR         14       PGNT#       I         15       PREQ#       O         16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                         | 6   | VDDIO  | PWR  |

| 9 VDD PWR 10 RST# O 11 VSS GND 12 PCLK I 13 VDD PWR 14 PGNT# I 15 PREQ# O 16 VDDIO PWR 17 PME# O 18 AD31 I/O 19 AD30 I/O 20 VDD PWR 21 AD29 I/O 22 AD28 I/O 23 AD27 I/O 24 VSS GND 25 AD26 I/O 26 AD25 I/O 27 AD24 I/O 28 C/BE3# I/O 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7   | TESTO  | 0    |

| 10       RST#       O         11       VSS       GND         12       PCLK       I         13       VDD       PWR         14       PGNT#       I         15       PREQ#       O         16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                     | 8   | INTA#  | 0    |

| 11       VSS       GND         12       PCLK       I         13       VDD       PWR         14       PGNT#       I         15       PREQ#       O         16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                   | 9   | VDD    | PWR  |

| 12       PCLK       I         13       VDD       PWR         14       PGNT#       I         15       PREQ#       O         16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                  | 10  | RST#   | 0    |

| 13         VDD         PWR           14         PGNT#         I           15         PREQ#         O           16         VDDIO         PWR           17         PME#         O           18         AD31         I/O           19         AD30         I/O           20         VDD         PWR           21         AD29         I/O           22         AD28         I/O           23         AD27         I/O           24         VSS         GND           25         AD26         I/O           26         AD25         I/O           27         AD24         I/O           28         C/BE3#         I/O           29         IDSEL         I           30         VSS         GND           31         AD23         I/O           32         AD22         I/O                                                                                                                                                                                                                          | 11  | VSS    | GND  |

| 14       PGNT#       I         15       PREQ#       O         16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                               | 12  | PCLK   | I    |

| 15 PREQ# O 16 VDDIO PWR 17 PME# O 18 AD31 I/O 19 AD30 I/O 20 VDD PWR 21 AD29 I/O 22 AD28 I/O 23 AD27 I/O 24 VSS GND 25 AD26 I/O 26 AD25 I/O 27 AD24 I/O 28 C/BE3# I/O 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13  | VDD    | PWR  |

| 16       VDDIO       PWR         17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14  | PGNT#  | I    |

| 17       PME#       O         18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15  | PREQ#  | 0    |

| 18       AD31       I/O         19       AD30       I/O         20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16  | VDDIO  | PWR  |

| 19 AD30 I/O 20 VDD PWR 21 AD29 I/O 22 AD28 I/O 23 AD27 I/O 24 VSS GND 25 AD26 I/O 26 AD25 I/O 27 AD24 I/O 28 C/BE3# I/O 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17  | PME#   | 0    |

| 20       VDD       PWR         21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18  | AD31   | I/O  |

| 21       AD29       I/O         22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19  | AD30   | I/O  |

| 22       AD28       I/O         23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20  | VDD    | PWR  |

| 23       AD27       I/O         24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21  | AD29   | I/O  |

| 24       VSS       GND         25       AD26       I/O         26       AD25       I/O         27       AD24       I/O         28       C/BE3#       I/O         29       IDSEL       I         30       VSS       GND         31       AD23       I/O         32       AD22       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22  | AD28   | I/O  |

| 25 AD26 I/O 26 AD25 I/O 27 AD24 I/O 28 C/BE3# I/O 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23  | AD27   | I/O  |

| 26 AD25 I/O 27 AD24 I/O 28 C/BE3# I/O 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24  | VSS    | GND  |

| 27 AD24 I/O 28 C/BE3# I/O 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25  | AD26   | I/O  |

| 28 C/BE3# I/O 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26  | AD25   | I/O  |

| 29 IDSEL I 30 VSS GND 31 AD23 I/O 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27  | AD24   | I/O  |

| 30         VSS         GND           31         AD23         I/O           32         AD22         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28  | C/BE3# | I/O  |

| 31 AD23 I/O<br>32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29  | IDSEL  | I    |

| 32 AD22 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30  | VSS    | GND  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31  | AD23   | I/O  |

| 33 AD21 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32  | AD22   | I/O  |

| 1/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33  | AD21   | I/O  |

| 34 AD20 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34  | AD20   | I/O  |

|            | •       |      |

|------------|---------|------|

| Pin<br>No. | Signal  | Туре |

| 35         | VDD     | PWR  |

| 36         | AD19    | I/O  |

| 37         | AD18    | I/O  |

| 38         | AD17    | I/O  |

| 39         | VDDIO   | PWR  |

| 40         | AD16    | I/O  |

| 41         | C/BE2#  | I/O  |

| 42         | VSS     | GND  |

| 43         | FRAME#  | I/O  |

| 44         | IRDY#   | I/O  |

| 45         | TRDY#   | I/O  |

| 46         | VDD     | PWR  |

| 47         | DEVSEL# | I/O  |

| 48         | STOP#   | I/O  |

| 49         | PERR#   | I/O  |

| 50         | VSS     | GND  |

| 51         | SERR#   | I/O  |

| 52         | PAR     | I/O  |

| 53         | C/BE1#  | I/O  |

| 54         | AD15    | I/O  |

| 55         | VDD     | PWR  |

| 56         | AD14    | I/O  |

| 57         | AD13    | I/O  |

| 58         | AD12    | I/O  |

| 59         | AD11    | I/O  |

| 60         | VSS     | GND  |

| 61         | AD10    | I/O  |

| 62         | AD9     | I/O  |

| 63         | VDDIO   | PWR  |

| 64         | AD8     | I/O  |

| 65         | C/BE0#  | I/O  |

| 66         | AD7     | I/O  |

| 67         | AD6     | I/O  |

| 68         | AD5     | I/O  |

| Pin<br>No. | Signal  | Туре |

|------------|---------|------|

| 69         | AD4     | I/O  |

| 70         | VDD     | PWR  |

| 71         | AD3     | I/O  |

| 72         | AD2     | I/O  |

| 73         | AD1     | I/O  |

| 74         | AD0     | I/O  |

| 75         | VSS     | GND  |

| 76         | TESTEN# | I    |

| 77         | CCLKO   | 0    |

| 78         | CCLKI   | I    |

| 79         | DIRECT  | _    |

| 80         | VDD     | PWR  |

| 81         | DATA7   | I/O  |

| 82         | DATA6   | I/O  |

| 83         | VSS     | GND  |

| 84         | DATA5   | I/O  |

| 85         | DATA4   | I/O  |

| 86         | DATA3   | I/O  |

| 87         | VDDIO   | PWR  |

| 88         | DATA2   | I/O  |

| 89         | DATA1   | I/O  |

| 90         | DATA0   | I/O  |

| 91         | VDD     | PWR  |

| 92         | CTRL1   | I/O  |

| 93         | CTRL0   | I/O  |

| 94         | VSS     | GND  |

| 95         | SCLK    | ı    |

| 96         | VDD     | PWR  |

| 97         | LREQ    | 0    |

| 98         | LNKON   | -    |

| 99         | LPS     | 0    |

| 100        | VSS     | GND  |

Table 2-3. Pin Assignment - Sorted Alphabetically

|        |      | Table      |

|--------|------|------------|

| Signal | Туре | Pin<br>No. |

| AD0    | I/O  | 74         |

| AD1    | I/O  | 73         |

| AD10   | I/O  | 61         |

| AD11   | I/O  | 59         |

| AD12   | I/O  | 58         |

| AD13   | I/O  | 57         |

| AD14   | I/O  | 56         |

| AD15   | I/O  | 54         |

| AD16   | I/O  | 40         |

| AD17   | I/O  | 38         |

| AD18   | I/O  | 37         |

| AD19   | I/O  | 36         |

| AD2    | I/O  | 72         |

| AD20   | I/O  | 34         |

| AD21   | I/O  | 33         |

| AD22   | I/O  | 32         |

| AD23   | I/O  | 31         |

| AD24   | I/O  | 27         |

| AD25   | I/O  | 26         |

| AD26   | I/O  | 25         |

| AD27   | I/O  | 23         |

| AD28   | I/O  | 22         |

| AD29   | I/O  | 21         |

| AD3    | I/O  | 71         |

| AD30   | I/O  | 19         |

| AD31   | I/O  | 18         |

| AD4    | I/O  | 69         |

| AD5    | I/O  | 68         |

| AD6    | I/O  | 67         |

| AD7    | I/O  | 66         |

| AD8    | I/O  | 64         |

| AD9    | I/O  | 62         |

| C/BE0# | I/O  | 65         |

| C/BE1# | I/O  | 53         |

| Signal  | Туре | Pin<br>No. |

|---------|------|------------|

| C/BE2#  | I/O  | 41         |

| C/BE3#  | I/O  | 28         |

| CCLKI   | I    | 78         |

| CCLKO   | 0    | 77         |

| CMC     | 0    | 2          |

| CMCL    | 0    | 3          |

| CTRL0   | I/O  | 93         |

| CTRL1   | I/O  | 92         |

| DATA0   | I/O  | 90         |

| DATA1   | I/O  | 89         |

| DATA2   | I/O  | 88         |

| DATA3   | I/O  | 86         |

| DATA4   | I/O  | 85         |

| DATA5   | I/O  | 84         |

| DATA6   | I/O  | 82         |

| DATA7   | I/O  | 81         |

| DEVSEL# | I/O  | 47         |

| DIRECT  | I    | 79         |

| EECLK   | 0    | 4          |

| EEDATA  | 1    | 5          |

| FRAME#  | I/O  | 43         |

| IDSEL   | I    | 29         |

| INTA#   | 0    | 8          |

| IRDY#   | I/O  | 44         |

| LNKON   | I    | 98         |

| LPS     | 0    | 99         |

| LREQ    | 0    | 97         |

| PAR     | I/O  | 52         |

| PCLK    | 1    | 12         |

| PERR#   | I/O  | 49         |

| PGNT#   | I    | 14         |

| PME#    | 0    | 17         |

| PREQ#   | 0    | 15         |

| RST#    | 0    | 10         |

| Signal  | Туре | Pin<br>No. |

|---------|------|------------|

| SCLK    | I    | 95         |

| SERR#   | I/O  | 51         |

| STOP#   | I/O  | 48         |

| TESTEN# | I    | 76         |

| TESTO   | 0    | 7          |

| TRDY#   | I/O  | 45         |

| VDD     | PWR  | 9          |

| VDD     | PWR  | 13         |

| VDD     | PWR  | 20         |

| VDD     | PWR  | 35         |

| VDD     | PWR  | 46         |

| VDD     | PWR  | 55         |

| VDD     | PWR  | 70         |

| VDD     | PWR  | 80         |

| VDD     | PWR  | 91         |

| VDD     | PWR  | 96         |

| VDDIO   | PWR  | 6          |

| VDDIO   | PWR  | 16         |

| VDDIO   | PWR  | 39         |

| VDDIO   | PWR  | 63         |

| VDDIO   | PWR  | 87         |

| VSS     | GND  | 1          |

| VSS     | GND  | 11         |

| VSS     | GND  | 24         |

| VSS     | GND  | 30         |

| VSS     | GND  | 42         |

| VSS     | GND  | 50         |

| VSS     | GND  | 60         |

| VSS     | GND  | 75         |

| VSS     | GND  | 83         |

| VSS     | GND  | 94         |

| VSS     | GND  | 100        |

# 2.2 SIGNAL DESCRIPTIONS

# 2.2.1 PCI Bus Interface Signals

| Signal Name | Pin No.     | Type | Description                                                                                                                                                 |

|-------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]    | Refer to    | I/O  | Multiplexed Address and Data                                                                                                                                |

|             | Table 2-3   |      | AD[31:0] is a physical address during the first clock of a PCI transaction; it is the data during subsequent clocks.                                        |

|             |             |      | When the CS4210 is a PCI master, AD[31:0] are outputs during the address and write data phases, and are inputs during the read data phase of a transaction. |

|             |             |      | When the CS4210 is a PCI slave, AD[31:0] are inputs during the address and write data phases, and are outputs during the read data phase of a transaction.  |

| C/BE[3:0]#  | 65, 53, 41, | I/O  | Bus Command and Byte Enables                                                                                                                                |

|             | 28          |      | Multiplexed bus command and byte enables.                                                                                                                   |

| FRAME#      | 43          | I/O  | Cycle Frame                                                                                                                                                 |

|             |             |      | Driven by the initiator to indicate the beginning and duration of an access.                                                                                |

| IRDY#       | 44          | I/O  | Initiator Ready                                                                                                                                             |

|             |             |      | Indicates that the initiator is ready to complete the current data phase of the transaction.                                                                |

| TRDY#       | 45          | I/O  | Target Ready                                                                                                                                                |

|             |             |      | Indicates that the current data phase of the transaction is ready to be completed.                                                                          |

| STOP#       | 48          | I/O  | Stop                                                                                                                                                        |

|             |             |      | Indicates that the current target is requesting the initiator to stop the current transaction.                                                              |

| DEVSEL#     | 47          | I/O  | Device Select                                                                                                                                               |

|             |             |      | When actively driven, DEVSEL# indicates the driving device has decoded its address as the target of the current access.                                     |

| IDSEL       | 29          | I    | Initialization Device Select                                                                                                                                |

|             |             |      | Used as a chip select during configuration read and write transactions.                                                                                     |

| PERR#       | 49          | I/O  | Parity Error                                                                                                                                                |

|             |             |      | Used for reporting data parity errors during all PCI transactions except a Special Cycle.                                                                   |

| SERR#       | 51          | I/O  | System Error                                                                                                                                                |

|             |             |      | Used for reporting address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic. |

| PAR         | 52          | I/O  | Parity                                                                                                                                                      |

|             |             |      | PAR is even parity across AD[31:0] and C/BE[3:0]. PAR is an input when AD[31:0] are inputs and is an output when AD[31:0] are outputs.                      |

| PREQ#       | 15          | 0    | PCI Bus Request                                                                                                                                             |

|             |             |      | PCI bus request to PCI bus arbiter.                                                                                                                         |

| PGNT#       | 14          | I    | PCI Bus Grant                                                                                                                                               |

|             |             |      | PCI bus grant from PCI bus arbiter.                                                                                                                         |

| INTA#       | 8           | 0    | Interrupt A                                                                                                                                                 |

|             |             |      | 1394 OpenHCI PCI interrupt.                                                                                                                                 |

# 2.2.1 PCI Bus Interface Signals (Continued)

| Signal Name | Pin No. | Туре | Description                                                                                     |  |

|-------------|---------|------|-------------------------------------------------------------------------------------------------|--|

| RST#        | 10      | I    | PCI Reset                                                                                       |  |

|             |         |      | RST# is driven low to reset the device.                                                         |  |

| PCLK        | 12      | I    | Clock                                                                                           |  |

|             |         |      | 0-33 MHz PCI clock.                                                                             |  |

| PME#        | 17      | 0    | Power Management Event                                                                          |  |

|             |         |      | PCI power management pin as defined in the PCI Bus Power Management Specification Revision 1.1. |  |

# 2.2.2 PHY-Link Interface Signals

| Signal Name | Pin No.               | I/O | Description                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA[0:7]   | 81, 82, 84,           | I/O | PHY Data                                                                                                                                                                                                                                                                                                          |

|             | 85, 86, 88,<br>89, 90 |     | Bidirectional data lines driven by both the Link and PHY layer modules. The width of the data bus depends on the speed of data transfer rate. Packet rate for 100 Mbit/sec transfers use DATA[0:1], 200 Mbit/sec transfers use DATA[0:3], 400 Mbit/sec transfers use DATA[0:7].                                   |

|             |                       |     | <b>Note:</b> DATA0 is considered the MSB (most significant bit) based upon the IEEE 1394-1995 specification.                                                                                                                                                                                                      |

| CTRL[0:1]   | 93, 92                | I/O | Control bits 1 and 0                                                                                                                                                                                                                                                                                              |

|             |                       |     | Bidirectional handshaking signals driven by both the Link and PHY layer modules. The CS4210 and CS4103 use these signals to arbitrate the control of the PHY-Link interface. The control bits also indicate the type of transfer communicating between the two layers namely idle, status, receive, and transmit. |

| LREQ        | 97                    | 0   | Link Request                                                                                                                                                                                                                                                                                                      |

|             |                       |     | Used by the CS4210 to request access of the 1394 bus and to read/write the internal registers of the CS4103.                                                                                                                                                                                                      |

| SCLK        | 95                    | I   | Sync Clock                                                                                                                                                                                                                                                                                                        |

|             |                       |     | The 49.152 MHz clock input driven by the CS4103's PLL block synchronized to the 1394 bus clock. This clock is also used to synchronize the LREQ, CTRL[0:1], and DATA[0:7] communication protocol between the CS4210 and CS4103.                                                                                   |

| LPS         | 99                    | 0   | Link Power Status                                                                                                                                                                                                                                                                                                 |

|             |                       |     | Indicates the power status of the CS4210. If LPS is low indicating the CS4210 is not powered, the signals CTRL[0:1], DATA[0:7], and SCLK connected to the CS4210 are disabled.                                                                                                                                    |

| LNKON       | 98                    | I   | Link On                                                                                                                                                                                                                                                                                                           |

|             |                       |     | Indicates to the CS4210 that the CS4103 has received a Link-On packet addressed to this node.                                                                                                                                                                                                                     |

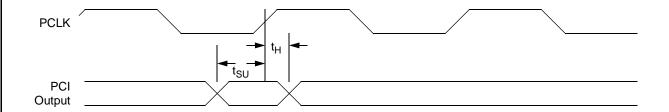

| DIRECT      | 79                    | I   | Direct                                                                                                                                                                                                                                                                                                            |